hello liu,

I have the same problem as you.

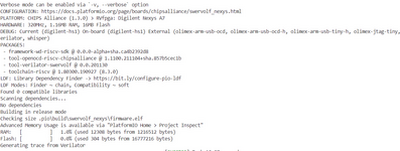

Installed verialtor on a windows system using Cygwin. gcc-core 11.4 ,verilator v4.228

the report shows success, but the vcd wave file is not generated in the folder

It is now no longer possible to install previous versions of gcc on cygwin

May I ask how to run the Vrvfpgasim.exe directly in the cygwin terminal by inlucding the +ram_init_file and +vcd=1

hello, dchaver,

I have the same problem.

Installed verialtor on a windows system using Cygwin. gcc-core 11.4 ,verilator v4.228

the report shows success, but the vcd wave file is not generated in the folder

It doesn't seem to be possible to install previous versions of gcc-10.2 on cygwin

Hi delete,

In v3.0 of RVfpga that we released a couple of months ago (you can obtain it at: https://university.imgtec.com/rvfpga-el2-v3-0-english-downloads-page/) we have added the following note. Can you please try it and let us know if it resolves your problem?

Best regards

Dani

Hi, Dani,

Thanks to reply.

I submitted an application before but didn't get it. I'm trying again now but it's under review

While waiting I would like to ask the following can you please provide the file Vrvfpgasim.exe conveniently. I would like to try and see if there is something wrong with my Vrvfpgasim.exe file.

Best regards

Delete

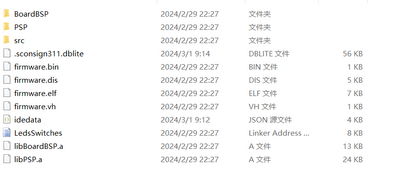

I think the problem is related with the cygwin libraries. In v3.0, inside the "RVfpgaEH1/RVfpga/verilatorSIM/OriginalBinaries/BinariesWindows" folder, you will find the .exe and the cygwin libraries. Meanwhile, can you try with these ones: https://drive.google.com/file/d/1hUuHPfQ9m1T8OiWDqexJpnJkleZQkIQ4/view?usp=drive_link

Thanks for the advice.

I have tried the exe file inside the "RVfpgaEH1/RVfpga/verilatorSIM/OriginalBinaries/BinariesWindows" and it is ok. But the exe file in that latter link still won't generate a vcd file. If I use the make command in the verilatorSIM folder in fpga 3.0 I will get an error. But in the original verilatorSIM there is no error, do I need to upgrade the verilator version. And if I directly replace those three files in cygwin libraries then the make command in cygwin will be wrong.

Can you try to generate the executable with make? You should be able to resolve the error with the instructions that I sent you in my first post.

If that does not work, I'll test it in my system and try to see what's happening.

Dani

So I understand you still don't have V3, right? I've asked you to be approved as soon as possible. When you get it, try in V3 to generate the binary and try to run it again.

I'm sorry to have disturbed you.

I have got v3

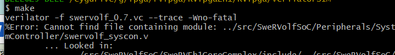

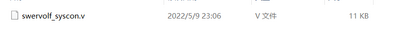

in v2: it is .v

in v3: it is .sv

so the error occurred

I don't know what went wrong.

if 'make' in v2's verilatorSIM, no errors and no .vcd file

if 'make' in v3's verilatorSIM, the error occurred.

In a few minutes I'll make some tests in my computer and let you know.

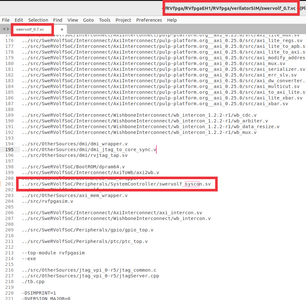

Can you try to rename in v3 from "swervolf_syscon.v" to "swervolf_syscon.sv" in file "RVfpga/RVfpgaEH1/RVfpga/verilatorSIM/swervolf_0.7.vc"?

Thanks again

Wow! ‘make' worked successfully.

But the generated .exe file still can't generate a .vcd file in V3. It's so confusing.