So I'm working my way through RVfpga Lab11 on the basics of SweRV EH-1 architecture and I have a question. The example simulator trace (Section 6) explains the signal changes as through the different pipelines stages of the processor, but something seems strange to me. If you look at the signals for rd0, .., rd4, they read as

我正在通过 RVfpga Lab11 学习 SweRV EH-1 架构的基础知识,我有一个问题。 示例模拟器跟踪(第 6 节)解释了通过处理器的不同管道阶段的信号变化,但对我来说有些事情似乎很奇怪。 如果您查看 rd0、..、rd4 的信号,它们会读作

rd0 = 0x0000006A // value in 0x29

rd1 = 0x0000006A // value in 0x29

rd2 = 0x0000006C // value in 0x30

rd3 = 0x00000001 // value in 0x31

li x29, 0x2

li x30, 0x4

li x31, 0x1

so I would expect these registers to read as

rd1 = 0x00000002

rd2 = 0x00000004

rd3 = 0x00000001

Hi Martiall,

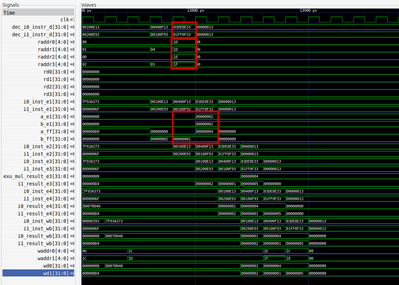

Note that those that you mention are the initial values, which are only used in the first iteration of the loop. If you look at the first iteration, you'll find those values (see attached image).

请注意,您提到的那些是初始值,仅在循环的第一次迭代中使用。 如果您查看第一次迭代,您将找到这些值(参见附图)。

However, in the loop body registers x28, x29 and x30 are updated, and in Lab 11 we are showing a random iteration where registers have already been updated.

In fact, you should not use the first iteration, where I$ misses happen and values are received through forwarding in this program, making the analysis more difficult.

Let us know if this resolves your question.

Best regards

Dani

Hey @dchaver

Thanks for your explanation, in hind sight I this should have been obvious to me but that's how it goes. I would just like to point out that in subsequent labs (e.g. Lab 12 Figure 3), the fact that this is not from the first iteration of the loop is made explicit in the text, and also in the figure labeling (e.g. Cycle i ,i + 5). If I could make a suggestion, you might consider doing the same here in case someone has a similar problem in the future.

感谢您的解释,事后看来,这对我来说应该是显而易见的,但事情就是这样。 我只想指出,在后续实验中(例如实验 12 图 3),文本中以及图形标签中都明确表明这不是来自循环的第一次迭代(e.g. Cycle i ,i + 5)。 如果我可以提出建议,您可以考虑在这里做同样的事情,以防将来有人遇到类似的问题。

Thanks for your help!

Martin